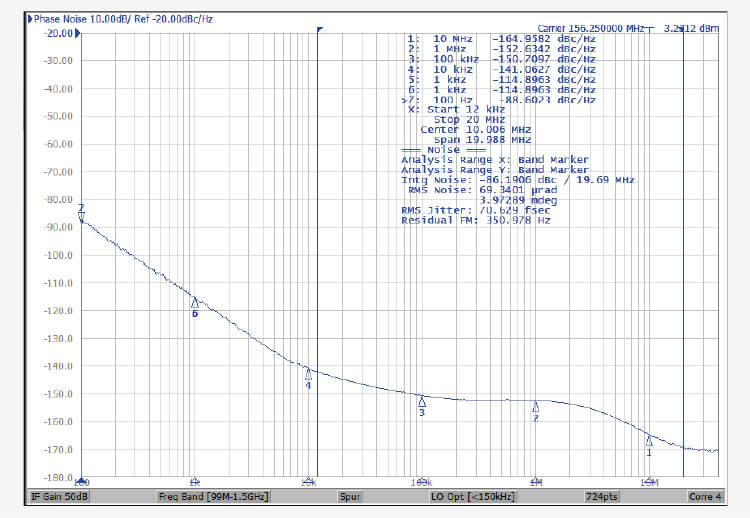

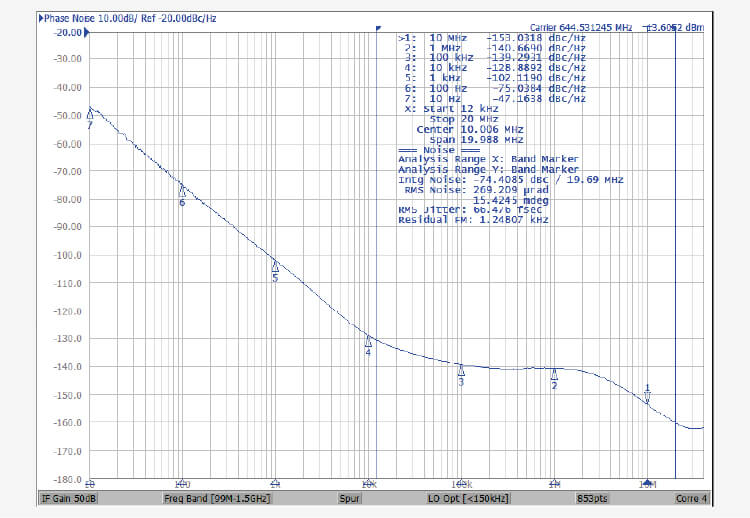

Ultra-low jitter offering down to 70 fsec

| Devices | Jitter Grade | Function | Key Features |

|---|---|---|---|

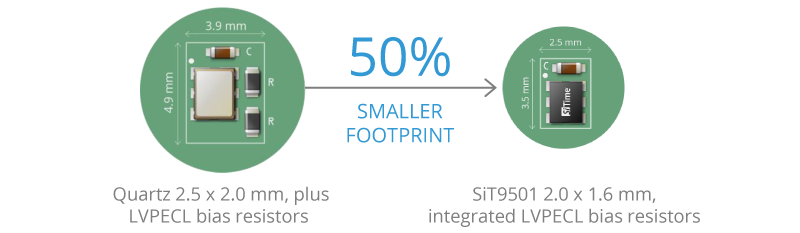

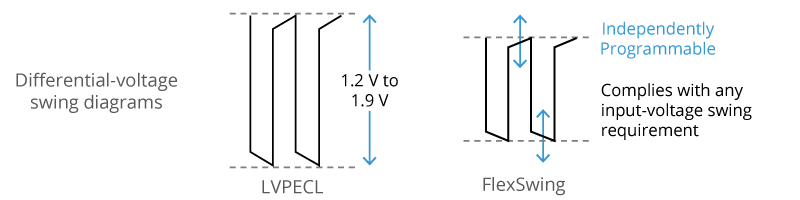

Differential XO SiT9501 25 to 644.53125 MHz | 70 fsec | Reference clock for high-speed PHYs | 14 standard frequencies, 105°C, 2016/2520/3225 pkgs. |

Differential XO SiT9375 25 to 644.53125 MHz | 200 fsec | Reference clock for high-speed PHYs | 31 standard frequencies, 105°C, 2016/2520/3225 pkgs. |

Differential XO | 230 fsec | Reference clock for high-speed PHYs | 1 to 725 MHz, 105°C, 3225/5032/7050 pkgs. |