AnDAPT 'WebAMP' Tool을 이용한 PCB면적 최적화 설계

AnDAPT 'WebAMP' Tool을 이용한 PCB면적 최적화 설계

- 2024-07-18

- AnDAPT

- 관리자

AnDAPT 고객이 빠른 생산을 가능하게 만들기 위해서 인기 있는 SoC용 기성품 PMIC 솔루션을 얻을 수 있는 소프트웨어 툴인 WebAmP R.D.(레퍼런스 디자인)를 통해 PCB면적 최적화 문제를 해결할수 있습니다.

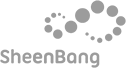

그림 1은 개발 보드 중 하나인 AmP8XEB1을 보여줍니다. 이 즉시 사용 가능한 평가 기판은 Xilinx Zynq 울트라스케일+(ZU+) MPSoC 제품군 FPGA 장치를 위한 전원 관리 솔루션을 보여줍니다. 새로운 설계를 생성하여 보드에 프로그래밍할 때마다 해당 PCB 면적과 BOM(부품 명세서)이 다시 생성되므로 고객은 최종 설계에 대한 정보를 사전에 얻을 수 있으며, WebAmP R.D.의 도움으로 기존 설계를 자유롭게 수정하도록 프로그래밍할 수 있습니다. PCB 면적 추정 및 자동 BOM 기능에 대해 자세히 알아보겠습니다.

Figure 1: Evaluation board for Xilinx Zynq UltraScale+ (ZU+) MPSoC family FPGA devices.

PCB 면적 추정에는 각 부품의 면적과 라우팅을 위한 추가 오버헤드(기본값은 부품 전체 면적의 25%)가 포함됩니다. 각 구성 요소의 면적은 x 및 y 치수를 곱하여 계산됩니다. 추정을 수행할 때 고려하는 주요 요소는 트레이스 폭, 컴포넌트 간 간격, 트레이스 간 간격 등입니다.

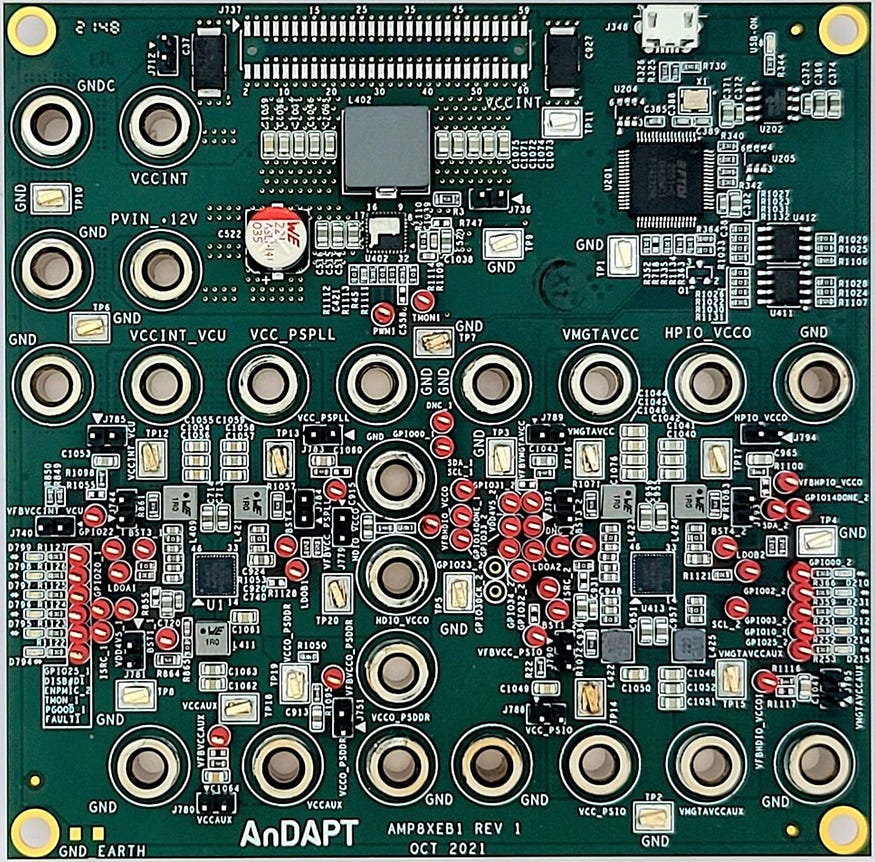

그림 2를 보면 50%, 75% 등 다양한 PCB 레이아웃 밀도/오버헤드를 선택할 수 있음을 알 수 있습니다. 레이아웃 밀도의 개념은 다음과 같이 설명할 수 있습니다. 구성 요소와 킵 아웃만 있는 경우 레이아웃 밀도는 100%로 간주됩니다. 레이아웃 밀도 100%의 보드 면적을 X라고 가정해 보겠습니다. 50% 및 75% 레이아웃 밀도의 해당 보드 면적은 각각 2배 및 1.33배입니다. 일반적으로 75%의 레이아웃 밀도가 최적으로 간주됩니다.

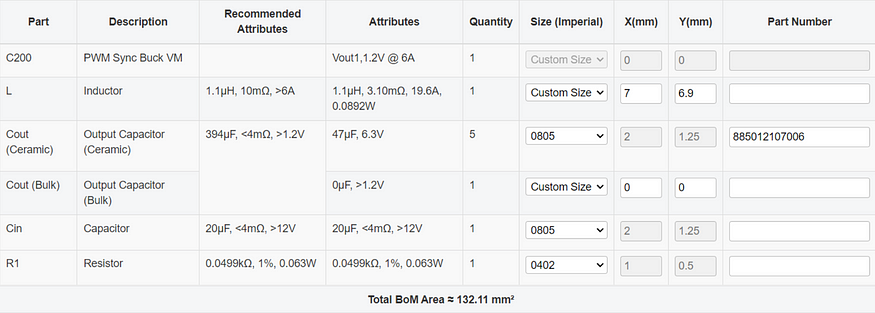

또한 PCB 면적 추정 기능은 자동 BOM 생성과 결합되어 있으며, 이는 WebAmP R.D.의 또 다른 중요한 기능입니다. 자동 생성된 BOM(Bill of Materials)은 시간과 리소스를 절약할 수 있습니다. AnDAPT WebAmP 소프트웨어에서 생성된 BOM은 다음과 같은 필수 세부 정보를 제공합니다:

1.부품 설명

2.부품 번호

3.수량

4.속성

그림 3은 자동 생성된 BOM을 보여줍니다. 이 소프트웨어는 PCB 면적 추정 외에도 부품 번호, 크기 등 고객에게 유용한 다른 정보도 제공합니다.

요약하면, WebAmP R.D.의 PCB 추정 기능을 통해 고객은 큰 노력 없이도 보드의 비용과 크기를 줄일 수 있습니다. 또한 자동 생성된 BOM은 시간을 절약하고 리소스를 최적화하며 실수 가능성을 줄여줍니다.

자세한 내용은 www.andapt.com 에서 확인하세요.

-

적용분야:

FPGA Power Solution